Definición

Es un mecanismo de cache de las traslaciones más utilizadas entre los pares virtuales a físicos.

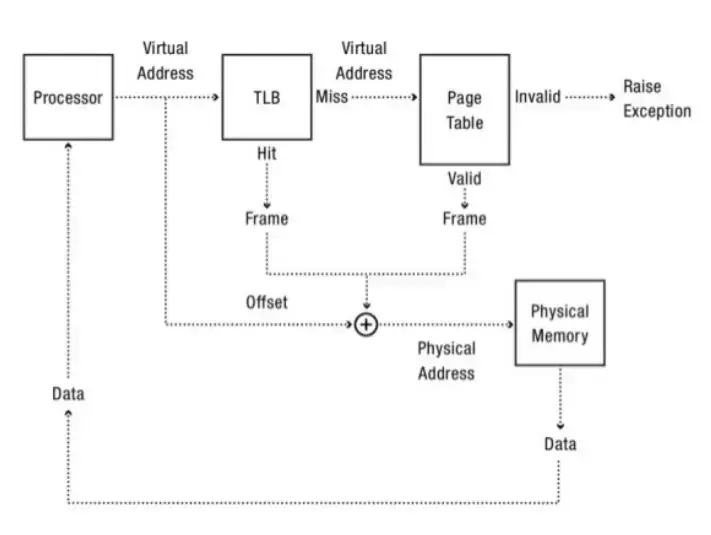

Por cada referencia a la memoria virtual, el hardware primero chequea la TLB para ver si esa traslación esta guardada ahí, si es así la traslación se hace rápidamente sin tener que consultar a la page table.

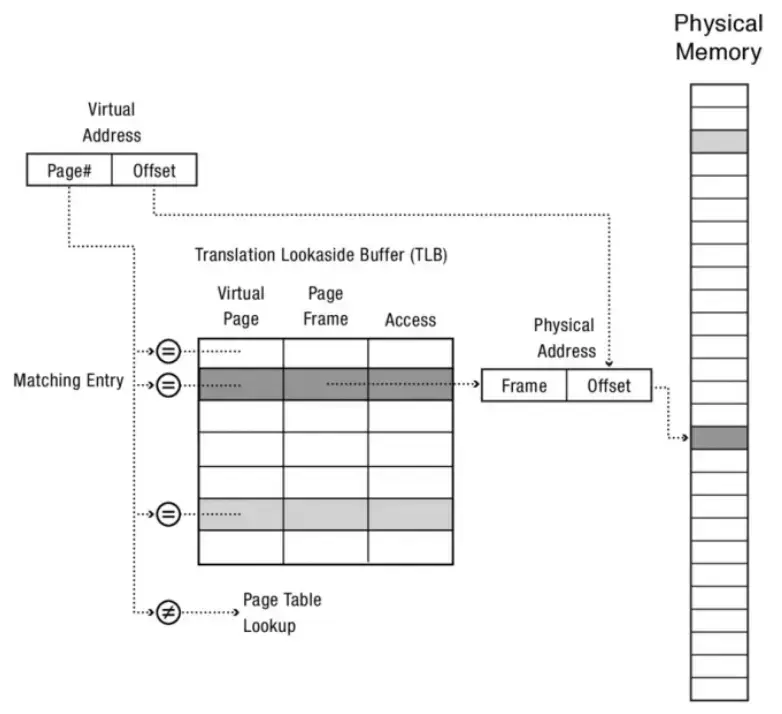

Este buffer es una pequeña tabla a nivel hardware que contiene los resultados de la recientes traslaciones de memoria realizadas. Cada entrada de la tabla mapea una virtual page a una physical page.

Normalmente se chequean todas las entradas del buffer contra la virtual page, si existe macheo el procesador utiliza ese macheo para formar la physical address, ahorrándose todos los pasos de la translación. Esto se lo conoce como TLB hit.

Cuando, del proceso anterior, no existe macheo en el TLB, se dice que se tiene un TLB miss.

Para que sea útil, la búsqueda de la TLB necesita ser mucho más rápido que realizar una traslación completa de una dirección de memoria. Por ende, las entradas de la tabla de la TLB son implementadas en una memoria muy rápida, memoria estática on chip, situada muy cerca del procesador. De hecho, para mantener esta búsqueda rápida, muchos sistemas en la actualidad incluyen múltiples niveles de TLB. En general cuanto más pequeña es la memoria, más rápida es la búsqueda

Consistencia de la TLB

Cada vez que se introduce un cache en el sistema, se necesita considerar la forma de asegurar la consistencia del cache con los datos originales cuando las entradas en el mismo son modificadas.

Para una ejecución correcta y segura de un programa, el sistema operativo tiene que asegurarse que cada programa ve su propia memoria y la de nadie más. Existen tres puntos a considerar

Context switch

Las direcciones virtuales del viejo proceso ya no son más válidas, y no deben ser válidas, para el nuevo proceso. De otra forma, el nuevo proceso sería capaz de leer las direcciones del viejo proceso.

Frente a un context switch, se necesita descartar el contenido de TLB. Este approach se denomina flush de TLB. Debido a que perder esta información no es útil, los procesadores agregan el id del proceso que produce cada traslación

Reducción de permiso

Cuando el sistema operativo modifica una entrada en una page table, el TBL por hardware no provee ninguna consistencia, ya que el mismo sistema operativo tiene la responsabilidad de mantenerla.

TLB Shutdown

En un sistema multiprocesador cada uno puede tener cacheada una copia de una translación en su TLB. Por ende, para seguridad y correctitud, cada vez que una entrada en la page table es modificada, la correspondiente entrada en todas las TLB de los procesadores tiene que ser descartada antes que los cambios tomen efecto.

Típicamente sólo el procesador actual puede invalidar su propia TLB, por ello, para eliminar una entrada en todos los procesadores del sistema, se requiere que el sistema operativo mande una interrupción a cada procesador y pida que esa entrada de la TLB sea eliminada. Esta es una operación muy costosa y por ende tiene su propio nombre y se denomina TLB shutdown

Que contiene

Una TLB típica puede tener entre 32, 64 o 128 entradas y ser lo que se llama fully associative. Básicamente esto quiere decir que cualquier traslación puede encontrarse en cualquier lado de la TLB. Una entrada de la TLB contiene los siguientes datos

- Virtual page number (VPN)

- Page frame number (PFN)

- bit de validez

- bits de protección

- dirty bit entre otros